Axes de recherche

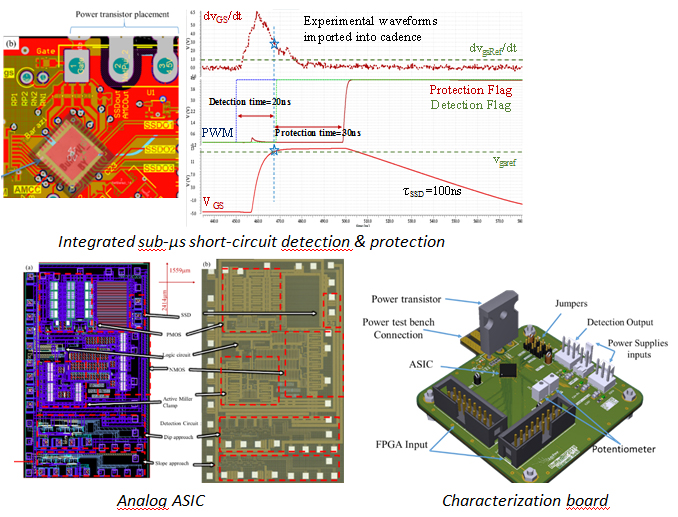

Axis 1 – Robust and Fast Short Circuit detection for MOSFET SiC Gate Driver

Technological barrier : Short-circuit detection method too low for WBG, presence of external DESAT component

Key parameters : WBG transistor with very fast turn-on / turn-off (100V/ns, 10A/ns)

Studies : Robust and Fast detection of Short-Circuit event at the IC Gate Driver level

Diagnostic using local Gate Driver signals

Optimized circuit implementation (driver & power die, PCB parasitic mitigation)

Recent NXP product

CMOS Integrated Circuit providing

new detection strategy opportunities & fast response

Optimized board implementation

Large bandwidth & fast response

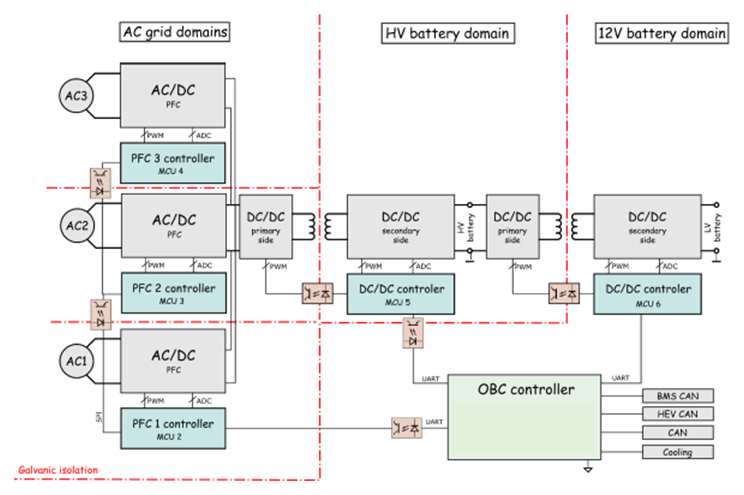

Axis 2-a) : Operational safety for EV powertrain (Charger, isolated DC / DC, Inverter)

Technological barrier : Fail-operational powertrain for Road Vehicles

Key parameters : 400 to 800V Li-Ion battery, high charge rate, 12 to 48V system

Studies : Solutions topology dependent (state-of-art ongoing)

400V fast charge, 12V or 24V applications, Si / SiC / GaN semiconductors

HV to few volts isolated DCDC Direct Conversion

DC/AC multi-leg inverter, fault tolerant, reconfiguration on-the-fly, default isolation

Centralized vs. distributed control strategies

3ph Combined Charging Unit

Isolated Phase Shifted Full Bridge

Axis 2-b) : PMIC High efficiency & Functional Safety

Technological barrier : Low cost, small size, uninterruptible µprocessor power supply

Key parameters : Fast time response, large bandwidth, µP supply voltage high accuracy

Studies : Multicellular topologies of converter for VRM

90V/1.3V direct conversion

Centralized vs. distributed control strategies

NEW Masterless IP

Decentralized

& Fail Operational

New decentralized control gives advantage:

- Fail Operational : Keep working while some phases are failing

- Discretize Power : allow more scalability

- Simplify : remove master

Combining strengths of high power efficiency

and system functional safety

Extend concept to avoid Single point failure

Goal : Fail Operational Supply of S32V25x & S32Ax – self detection & power optimization

Discretized Power for system modularity : easy reconfiguration & safe

5-cell GaN-based multiphase converter

using decentralized controllers in each phase

Optimized board implementation

Efficiency vs Output Current for different number of active cells N (48V /12V application).

Reconfigurability

Dynamic reconfiguration: from 4 to 3 active phases (2A/div; 2V/div; 200us/div)

Axis 3: EMC/EFT-aware architecture and design, from IC to module

Technological barrier : Ensure immunity to RF disturbance and maintain performance level and cost

Key parameters : High immunity to EMI and EFT, low RF emission, low cost, high performance (accuracy), Robustness

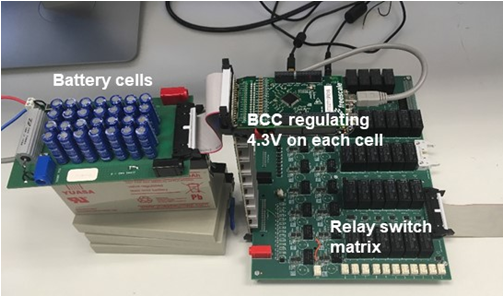

Studies : – Architecture and design of battery management system (BMS) integrated circuit (IC) to improve its immunity to electromagnetic disturbances and its emission

– Minimize the number of external filtering devices

– Develop models and simulation test bench to predict RF and ESD immunity

ESD network 1st GEN of BMS

Test of robustness vs EFT

during hot plug connections

Stacks cells are plugged randomly, Each capacitor in parallel with the battery can discharge in the IC and create damage. Hundreds of combinations tested with 14 cells.

Test of robustness vs EFT

during hot plug connections

TLP curves of ESD network for BMS from 10V to 90V with stack battery cells 100nS square pulse until 3A

EMC tests for Automotive

Conducted Emission investigations of a BMS IC, in a Faraday cage